Campo di applicazione

1. Circuito integrato ad alta velocità

2. Dispositivi a microonde

3. Circuito integrato ad alta temperatura

4. Dispositivi di alimentazione

5. Circuito integrato a basso consumo

6. MEMS

7. Circuito integrato a bassa tensione

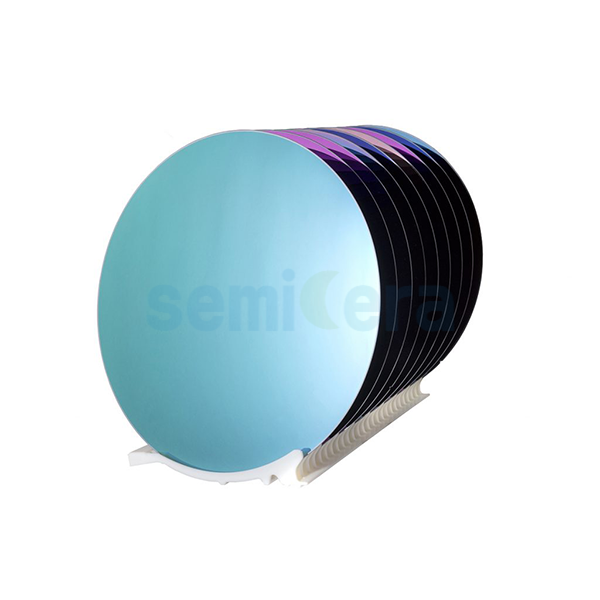

| Articolo | Discussione | |

| Complessivamente | Diametro del wafer | 50/75/100/125/150/200mm±25um |

| Arco/Deformazione | <10um | |

| Particelle | 0,3um<30 cad | |

| Piatti/tacca | Piatto o Notch | |

| Esclusione dei bordi | / | |

| Livello dispositivo | Tipo/drogante del livello del dispositivo | Tipo N/Tipo P |

| Orientamento a livello di dispositivo | <1-0-0> / <1-1-1> / <1-1-0> | |

| Spessore dello strato del dispositivo | 0,1~300um | |

| Resistività dello strato del dispositivo | 0,001~100.000 ohm-cm | |

| Particelle dello strato del dispositivo | <30ea@0.3 | |

| TTV livello dispositivo | <10um | |

| Finitura livello dispositivo | Lucido | |

| SCATOLA | Spessore dell'ossido termico sepolto | 50nm(500Å)~15um |

| Gestire il livello | Maniglia tipo wafer/drogante | Tipo N/Tipo P |

| Gestire l'orientamento del wafer | <1-0-0> / <1-1-1> / <1-1-0> | |

| Gestire la resistività del wafer | 0,001~100.000 ohm-cm | |

| Gestire lo spessore del wafer | >100um | |

| Maniglia Finitura Wafer | Lucido | |

| I wafer SOI con specifiche target possono essere personalizzati in base alle esigenze del cliente. | ||

-

Sabbia di quarzo

-

Anello in grafite rivestito in carburo di tantalio

-

Suscettore di crescita dei cristalli rivestito in carburo di silicio

-

Materiale in grafite ad alta densità in feltro duro di grafite

-

Carburo di silicio resistente alla corrosione Eff ceramico...

-

Paletta in carburo di silicio ad alta purezza